# Do HDL ao Silício: Explorando o Ecossistema Open Source

Julio Avelar

julio.avelar@students.ic.unicamp.br

#### Whoami

- Julio Nunes Avelar

- Estudante de Engenharia de Computação

- Um Viciado em Café, Ouvir Música,

RISC-V e FPGAs

- Hobby: Sim!

- Telegram: @jn513

- Site: bzoide.dev

- Github: JN513

- julio.avelar@students.ic.unicamp.br

#### Hostname

- Laboratório de Sistemas de Computação

- Embarcações

- Unicamp Odhin

# Por que o Design de Hardware digital importa?

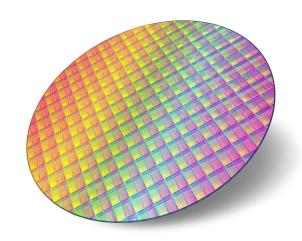

# Ser capaz de desenvolver e produzir Chips se torna algo de extrema importância.

- Independência tecnológica

- Segurança e confiabilidade

- Democratização do hardware

- Inovação e diferenciação

- Economia

# Como é realizado o Design de Hardware Digital atualmente?

- Mercado dominado por ferramentas proprietárias

- Synopsys, Cadence, Mentor, AMD/Xilinx, Altera

- Fluxo fechado e complexo

- Custo elevado

- Licenças caras, PDKs fechados, recursos de ensino limitados.

- Barreira de entrada elevada

- Pouca transparência.

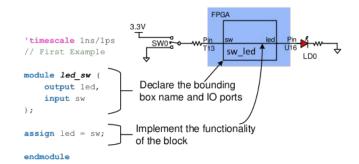

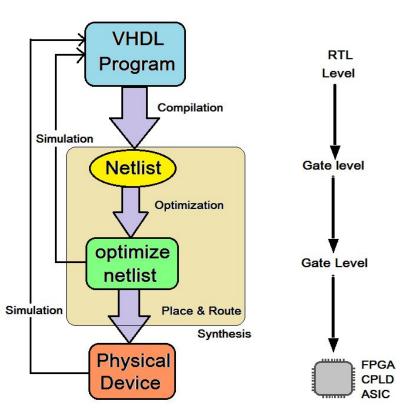

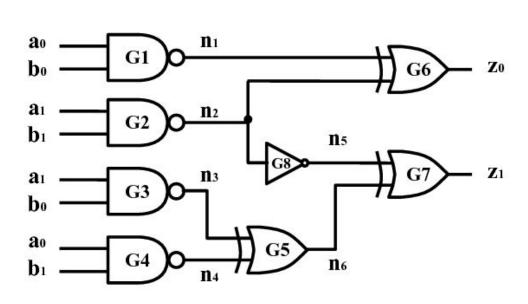

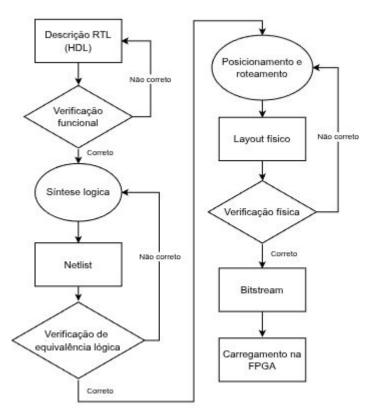

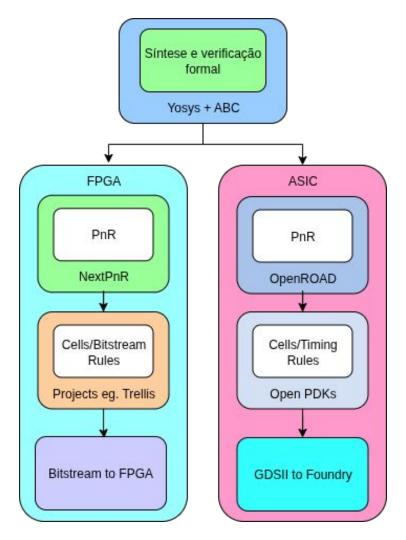

#### Como funciona o fluxo de desenvolvimento

- Descrição em HDL (Verilog/VHDL)

- Síntese

- Place and Route (PnR)

- Verificação

- Geração de Bitstream ou GDSII

#### Como funciona o fluxo de desenvolvimento

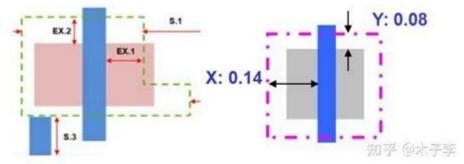

# O que é um PDK (Process Design Kit)?

- Conjunto de arquivos que descreve as regras do processo de fabricação (ex.: SkyWater 130 nm).

- Define as células padrão (standard cells): NAND, NOR, Flip-Flops, RAM, etc.

- Contém informações de layout, timing, consumo, restrições físicas.

- É usado pelas ferramentas EDA.

### O Início da Mudança - Yosys (2012)

- Criado em 2012 por Clifford Wolf

- Primeira ferramenta de síntese open source para Verilog

- Abriu o caminho para fluxos livres em FPGA e ASIC

- Pela primeira vez, o HDL podia ser sintetizado sem ferramentas proprietárias

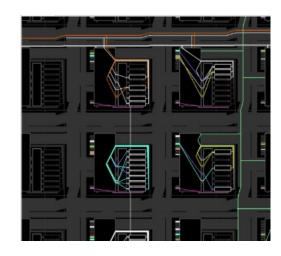

### Avanço no Mundo FPGA - NextPnR (2017)

- Fluxos abertos para FPGAs Lattice (iCE40, ECP5)

- Place & Route open source em dispositivos comerciais

- Tornou possível programar uma FPGA inteira com ferramentas livres

- Inicialmente Project IceStorm e prjTrellis

- Atualmente 8 projetos distintos para famílias de FPGAs distintas

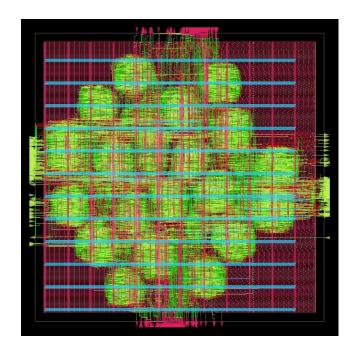

#### Avanço no Mundo FPGA - NextPnR

# nextpnr -- a portable FPGA place and route tool

nextpnr aims to be a vendor neutral, timing driven, FOSS FPGA place and route tool.

#### Currently nextpnr supports:

- Lattice iCE40 devices supported by Project IceStorm

- Lattice ECP5 devices supported by Project Trellis

- Lattice Nexus devices supported by Project Oxide

- Gowin LittleBee devices supported by Project Apicula

- NanoXplore NG-Ultra devices supported by <u>Project Beyond</u>

- (experimental) Cyclone V devices supported by Mistral

- (experimental) Lattice MachXO2 devices supported by Project Trellis

- (experimental) a "generic" back-end for user-defined architectures

# O Passo para os ASICs - OpenROAD (2018)

- Iniciativa da DARPA e de algumas universidades para criar um fluxo ASIC automatizado e open source.

- Conjunto de ferramentas cobrindo desde a síntese até o layout físico (RTL -> GDSII)

- Possui como meta executar um design em 24 horas.

#### O Marco Histórico - SkyWater 130 Open PDK (2020)

- Google + SkyWater liberam o primeiro PDK aberto (130 nm).

- Qualquer pessoa pode projetar e fabricar um ASIC de verdade.

- Novos players capazes de construir chips: Makers, Startups e entusiastas.

- Viabilizou iniciativas como o TinyTap out.

#### **Casos Reais**

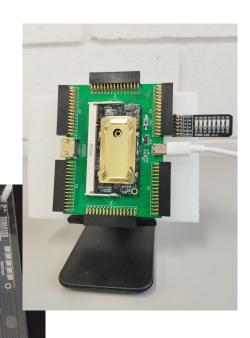

- TinyTapeout

- https://tinytapeout.com/

- Google / Efabless Shuttle Program

TinyTapeout Demo Board 📑

#### O Fluxo em Si

#### Uma breve demo

- Yosys + PrjTrellis

- Yosys + NextPnRXilinx

- OpenROAD + asap7

https://github.com/JN513/ohd\_2025\_demo

#### **Alguns Links**

- Yosys: <a href="https://github.com/YosysHQ/yosys">https://github.com/YosysHQ/yosys</a>

- NextPnR: <a href="https://github.com/YosysHQ">https://github.com/YosysHQ</a>

- OpenRoad: <a href="https://github.com/The-OpenROAD-Project/OpenROAD">https://github.com/The-OpenROAD-Project/OpenROAD</a>

- OpenLane: <a href="https://github.com/efabless/openlane2">https://github.com/efabless/openlane2</a>

- OpenFPGALoader: <a href="https://github.com/trabucayre/openFPGALoader">https://github.com/trabucayre/openFPGALoader</a>

- PrjTrellis: <a href="https://github.com/YosysHQ/prjtrellis">https://github.com/YosysHQ/prjtrellis</a>

- TinyTapeout: <a href="https://tinytapeout.com/">https://tinytapeout.com/</a>

- Manual:

- https://github.com/JN513/Utilizando-FPGAs-com-ferramentas-OpenSource

# **Obrigado! Perguntas?**

julio.avelar@students.ic.unicamp.br

# Link para essa apresentação